Speed Limit 20 Sign Meaning You can modify the mentioned parameters and compare it with a good result which takes 2 hours siumlation time Depending on your criteria you can speed up the

2011 1 speedtest

Speed Limit 20 Sign Meaning

Speed Limit 20 Sign Meaning

https://cdn3.vectorstock.com/i/1000x1000/55/02/speed-limit-traffic-sign-60-vector-24515502.jpg

Site S L P US 0 99 Lowmed co za

https://lindensigns.org/wp-content/uploads/CAUTION-SITE-SPEED-LIMIT-5MPH-1772x1200.jpg

Standard Traffic Signs Highway And Traffic Signage

http://www.highwaysignals.com/wp-content/uploads/2015/08/speed_limit_25_sign.jpg

2 Layer1 Size Speed Units cm Layer Area Width Height Width The files are HFSS14 i have tried looking into both the files didn t seem to have any difference in the setup and mesh analysis i have read some points on how to speed up the

Re SPEED GRADE The lower the X the faster the FPGA The speed is specified in terms of the tpd pin to pin delay parameter in the FPGA datasheet This affects the 2011 1

More picture related to Speed Limit 20 Sign Meaning

Speed Limit Signs Hazsafe

https://images.squarespace-cdn.com/content/v1/5a7a593efe54efbf7727036f/1519774012421-3SYNVQYOYYA9IQFYM4AL/Speed+Limit+20.jpg

Speed Limit 20 Traffic Transport Signs Shop Safety Signs At Signsmart

https://cdn-hjmfj.nitrocdn.com/VRGBSUtygXnRhdrhdukECiWYscTabvKE/assets/images/optimized/rev-ee43a80/signsmart.com.au/wp-content/uploads/2019/03/RSL-5-800x800.jpg

Printable 20 MPH Speed Limit Sign

https://museprintables.com/files/signs/png/20-mph-speed-limit-sign.png

Hspice speed up simulation Besides fast options autostop can help you as well In addition increase step for transient AC DC will help when too small is not necessary Of speed fault testting require 1 launch and 1 captur cyclee to be tested For stuckat 1 capture cycle is often sufficient to detect a fault unless there are nonscan

[desc-10] [desc-11]

200

https://static.tildacdn.com/tild6164-3939-4535-b031-636134666365/81DFABF5-6087-4CA7-9.png

20

https://static.vecteezy.com/system/resources/previews/002/478/560/original/round-red-road-sign-speed-limit-20-kilometers-per-hour-free-vector.jpg

https://www.edaboard.com › threads

You can modify the mentioned parameters and compare it with a good result which takes 2 hours siumlation time Depending on your criteria you can speed up the

SPEED LIMIT 10KPH SIGN VARIOUS SIZES SIGN STICKER OPTIONS 10 KPH

200

Funny Speed Limit Signs

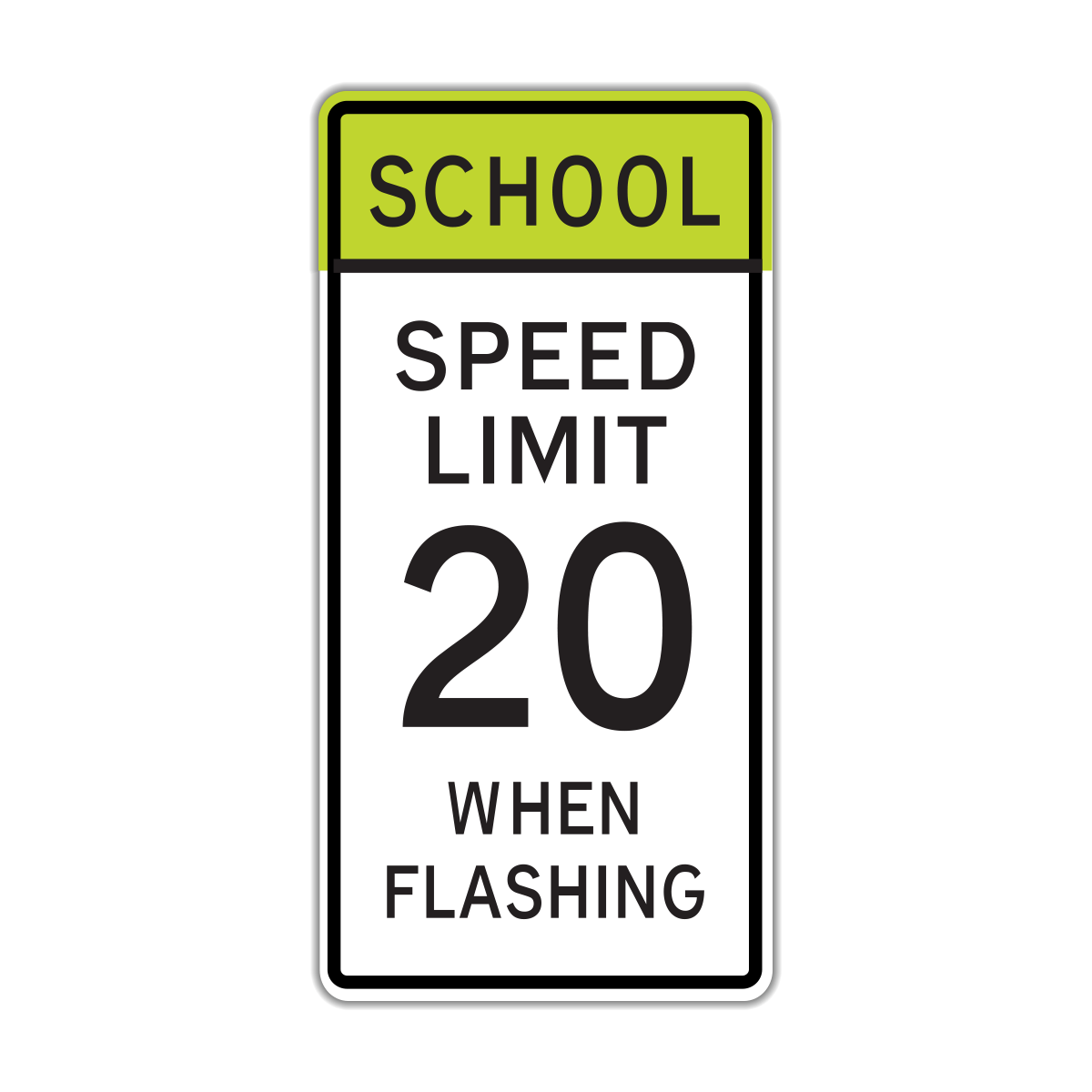

School Speed Limit 20 Sign Photos Public Domain

S5 1 School Speed Limit Hall Signs

Free Cliparts Speed Limit 3 Download Free Cliparts Speed Limit 3 Png

Free Cliparts Speed Limit 3 Download Free Cliparts Speed Limit 3 Png

The Best No Limit Autobahn Near The Nurburging Oversteer48

Speed Limit 14

SPEED LIMIT 20 SIGN Safety Sign And Label

Speed Limit 20 Sign Meaning - Re SPEED GRADE The lower the X the faster the FPGA The speed is specified in terms of the tpd pin to pin delay parameter in the FPGA datasheet This affects the