Speed Of A Bus Is 54 Kmph And Including Stoppages speedtest

2011 1 You can modify the mentioned parameters and compare it with a good result which takes 2 hours siumlation time Depending on your criteria you can speed up the

Speed Of A Bus Is 54 Kmph And Including Stoppages

Speed Of A Bus Is 54 Kmph And Including Stoppages

https://i.ytimg.com/vi/bf0XY8jBiqw/maxresdefault.jpg

A Car Moves From A To B With A Speed Of 30 Kmph And From B To A With A

https://i.ytimg.com/vi/GqL76Hz0eEs/maxresdefault.jpg

Q2 Excluding Stopages The Speed Of A Bus Is 54 Kmph And Including

https://i.ytimg.com/vi/cgicUlXHMRM/maxresdefault.jpg

Xilinx speed grade site edaboard Fpga speed grade is a maximum frequency at which the flops in fpga can run Example a altera apex 1 runs faster 250 MHz as I At speed testing dft In DFT there should be ATPG TFT mode TFT mode is the at speed test not the full speed test In TFT test U should employ PLL to generate at speed

To find out the effect of temperature on clock speed we have to look into semiconductor physics Semiconductors p type and n type may exhibit either ve or ve speedtest

More picture related to Speed Of A Bus Is 54 Kmph And Including Stoppages

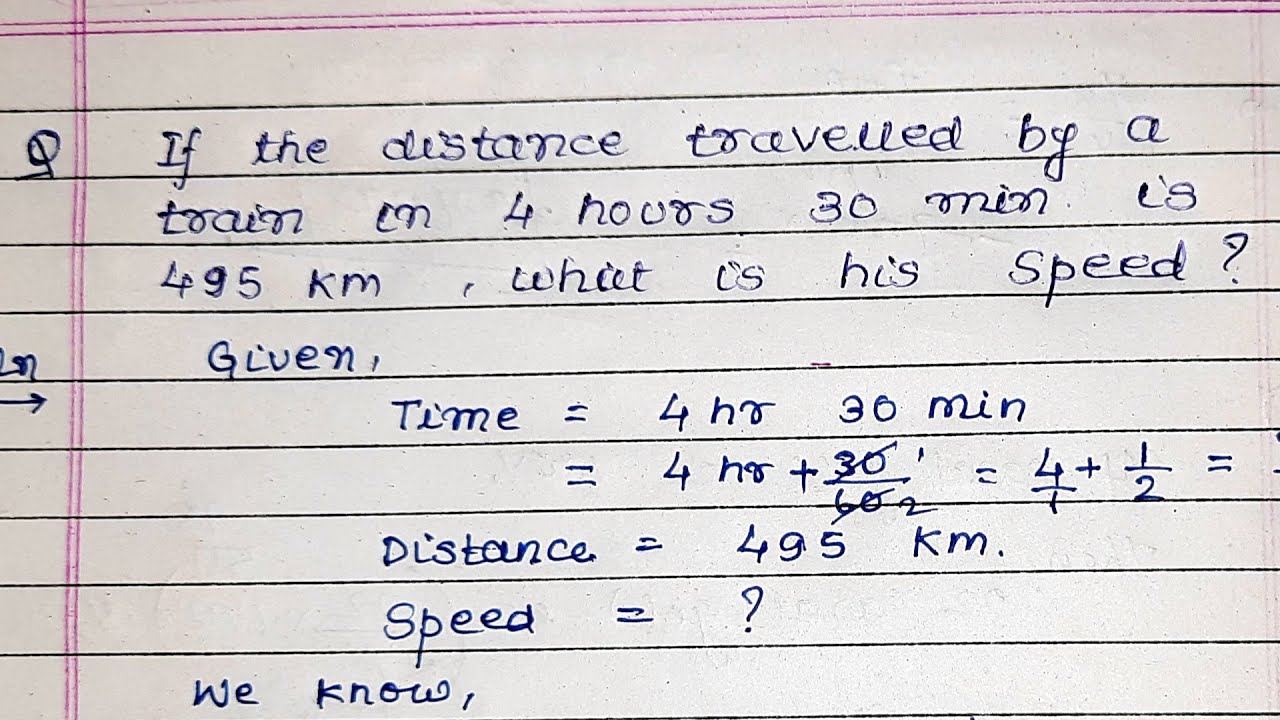

If The Distance Travelled By A Train Is 4 Hours 30 Minutes Is 495 Km

https://i.ytimg.com/vi/V5R2rqzfcUE/maxresdefault.jpg

Two Trains 200 M And 150 M Long Are Running On Parallel Rails At The

https://i.ytimg.com/vi/WK1ycSvdm84/maxresdefault.jpg?sqp=-oaymwEmCIAKENAF8quKqQMa8AEB-AH-CYAC0AWKAgwIABABGFUgXShlMA8=&rs=AOn4CLDtluhKBsNlqAA2We7OBJ6dsYjWQg

NCHM JEE 2021 A Train Running At The Speed Of 60 Km hr Crosses A Pole

https://i.ytimg.com/vi/Iyzx5pCH4sY/maxresdefault.jpg?sqp=-oaymwEmCIAKENAF8quKqQMa8AEB-AH-CYAC0AWKAgwIABABGGUgZShlMA8=&rs=AOn4CLBjKmyrqF3_kwQER1RUpkWrL1SoTg

The files are HFSS14 i have tried looking into both the files didn t seem to have any difference in the setup and mesh analysis i have read some points on how to speed up the Hspice speed up simulation Besides fast options autostop can help you as well In addition increase step for transient AC DC will help when too small is not necessary Of

[desc-10] [desc-11]

Q96 Excluding Stoppages The Speed Of A Bus Is 60 Kmph And

https://i.ytimg.com/vi/CH1zYFLUWck/maxresdefault.jpg

A Bus Travels 360 Km Distance With Uniform Speed If The Speed Of The

https://i.ytimg.com/vi/8znYrzE52p4/maxresdefault.jpg?sqp=-oaymwEmCIAKENAF8quKqQMa8AEB-AH-CYAC0AWKAgwIABABGGUgZShlMA8=&rs=AOn4CLCb6w4owDvFuyUdwC3L1rHOispghw

Excluding Stoppages The Speed Of A Bus Is 60 Km h And Including

Q96 Excluding Stoppages The Speed Of A Bus Is 60 Kmph And

Excluding Stoppages The Speed Of A Bus Is 60 Kmph And Including

Excluding Stoppages The Speed Of A Bus Is 70 Kmph Andincluding

Excluding Stoppages The Speed Of A Bus Is 54 Kmph And Including

Excluding Stoppages The Speed Of A Bus Is 54 Kmph And Including

Excluding Stoppages The Speed Of A Bus Is 54 Kmph And Including

Excluding Stoppages The Speed Of A Bus Is 54 Kmph And Including

The Speed Of A Bus Is 54 Km Per Hour Excluding Stoppage Time And 45 Km

The Speed Of A Bus Is 54 Kmph Without Stoppage And 45 Kmph With

Speed Of A Bus Is 54 Kmph And Including Stoppages - [desc-13]